# 16-bit Proprietary Microcontroller

**CMOS**

# F<sup>2</sup>MC-16LX MB90800 Series

## MB90802/802S/803/803S/F804/V800

#### DESCRIPTION

The MB90800 series is a general-purpose 16-bit microcontroller that has been developed for high-speed real-time processing required for industrial and office automation equipment and process control, etc. The LCD controller of 48 segment four common is built into.

Instruction set has taken over the same AT architecture as in the F<sup>2</sup>MC-8L and F<sup>2</sup>MC-16L, and is further enhanced to support high level languages, extend addressing mode, enhanced divide/multiply instructions with sign and enrichment of bit processing. In addition, long word processing is now available by introducing a 32-bit accumulator.

#### **■ FEATURES**

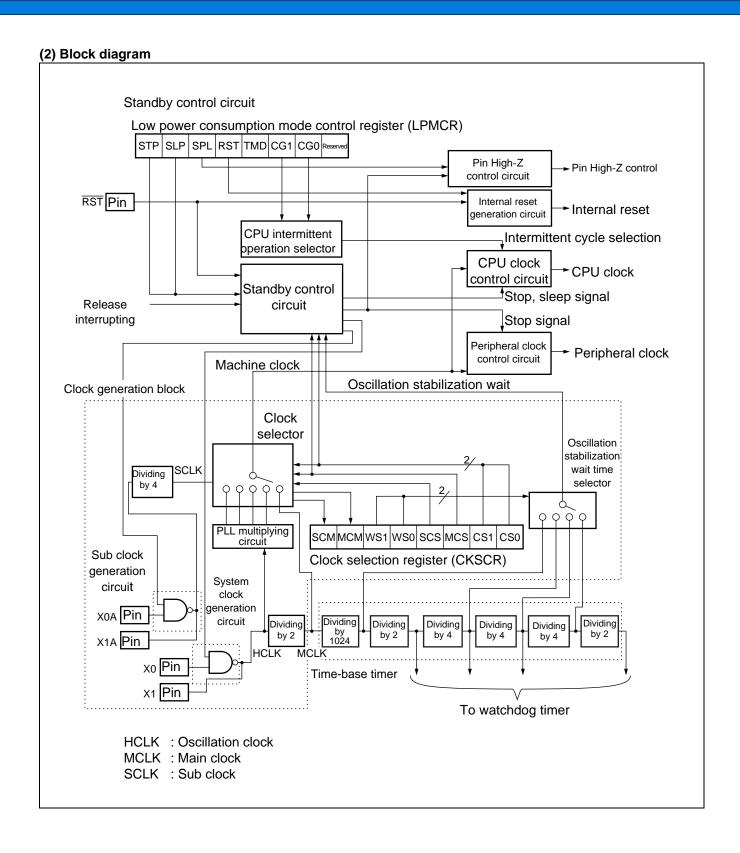

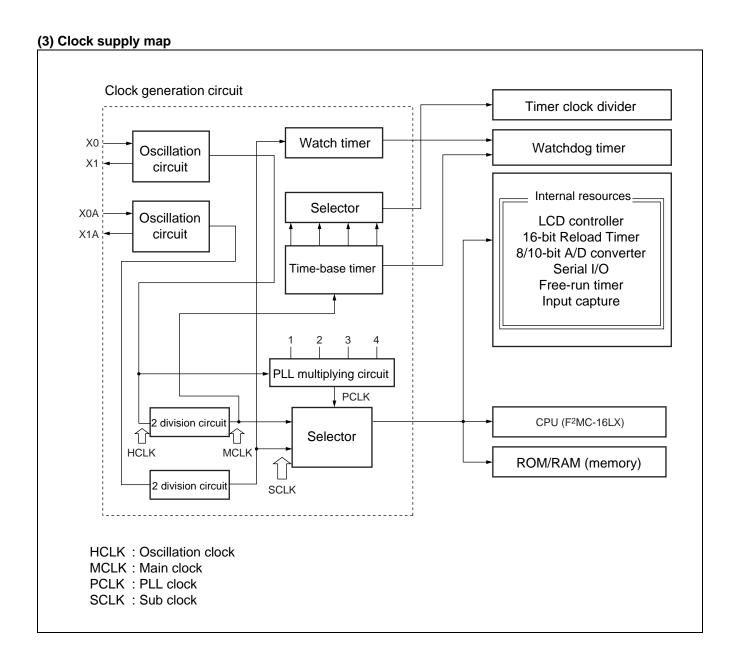

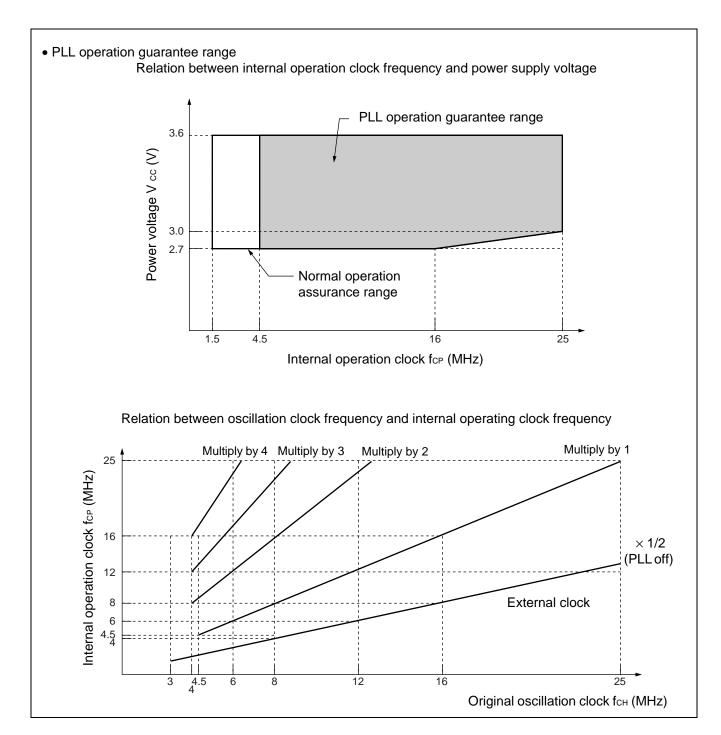

- Clock

- Built-in PLL clock frequency multiplication circuit

- Operating clock (PLL clock): divided-by-2 of oscillation (at oscillation of 6.25 MHz) or

1 to 4 times the oscillation (at oscillation of 6.25 MHz to 25 MHz).

- Minimum instruction execution time of 40.0 ns (at oscillation of 6.25 MHz, four times the PLL clock, operation at Vcc = 3.3 V)

- The maximum memory space:16 MB

- 24-bit internal addressing

- · Bank addressing

(Continued)

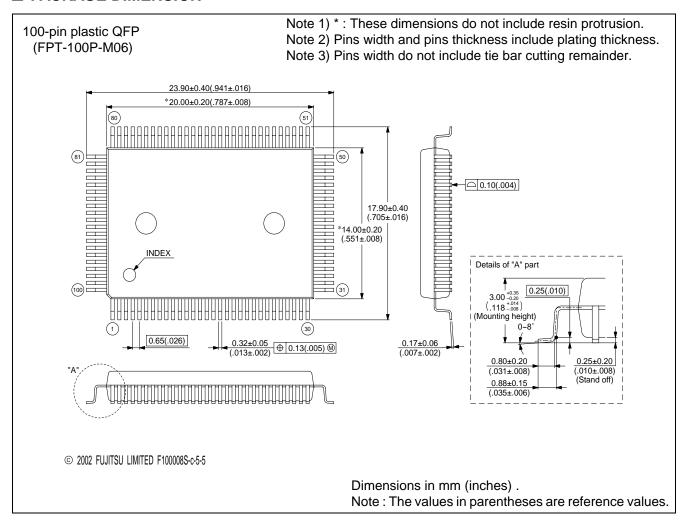

#### **■ PACKAGE**

#### (Continued)

#### • Optimized instruction set for controller applications

- Wide choice of data types (bit, byte, word, and long word)

- Wide choice of addressing modes (23 types)

- · High code efficiency

- Enhanced high-precision computing with 32-bit accumulator

- Enhanced Multiply/Divide instructions with sign and the RETI instruction

#### • Instruction system compatible with high-level language (C language) and multitask

- Employing system stack pointer

- Instruction set has symmetry and barrel shift instructions

#### Program Patch Function (2 address pointer)

#### • 4-byte instruction queue

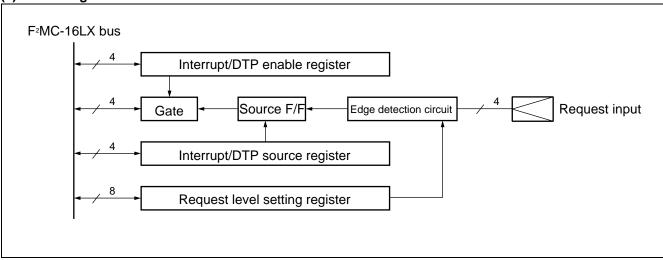

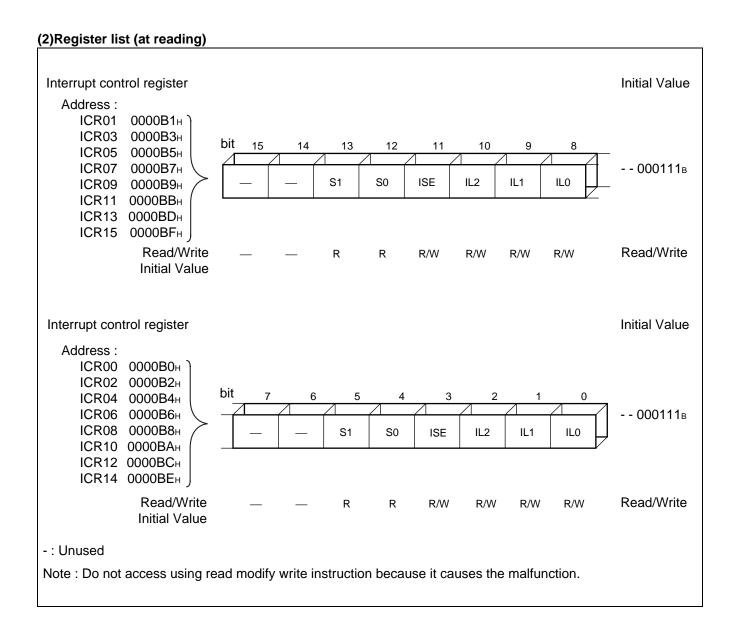

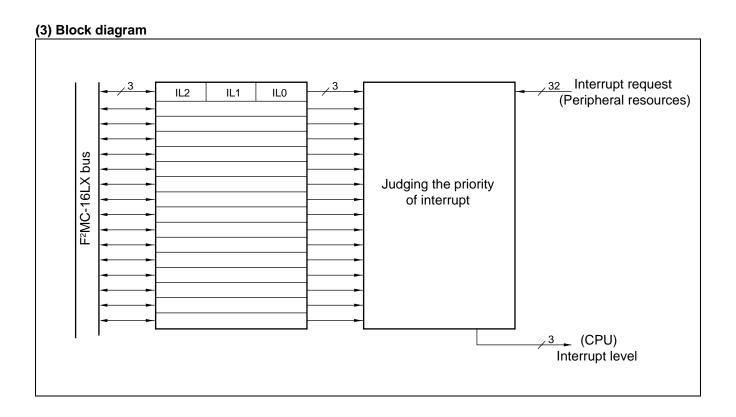

#### • Interrupt function

- The priority level can be set to programmable.

- Interrupt function with 32 factors

#### Data transfer function

• Expanded intelligent I/O service function (EI2OS): Maximum of 16 channels

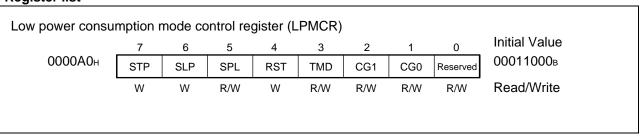

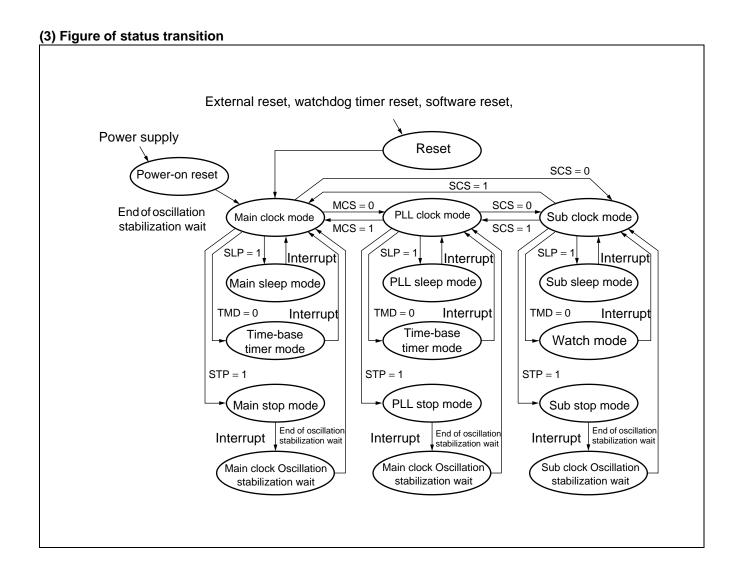

#### • Low Power Consumption Mode

- Sleep mode (a mode that halts CPU operating clock)

- Time-base timer mode (a mode that operates oscillation clock and time-base timer)

- Watch mode (mode in which only the subclock and watch timers operate)

- Stop mode (a mode that stops oscillation clock and sub clock)

- CPU blocking mode (operating CPU at each set cycle)

#### Package

• QFP-100 (FPT-100P-M06:0.65 mm pin pitch)

• Process : CMOS technology

### **■ PRODUCT LINEUP**

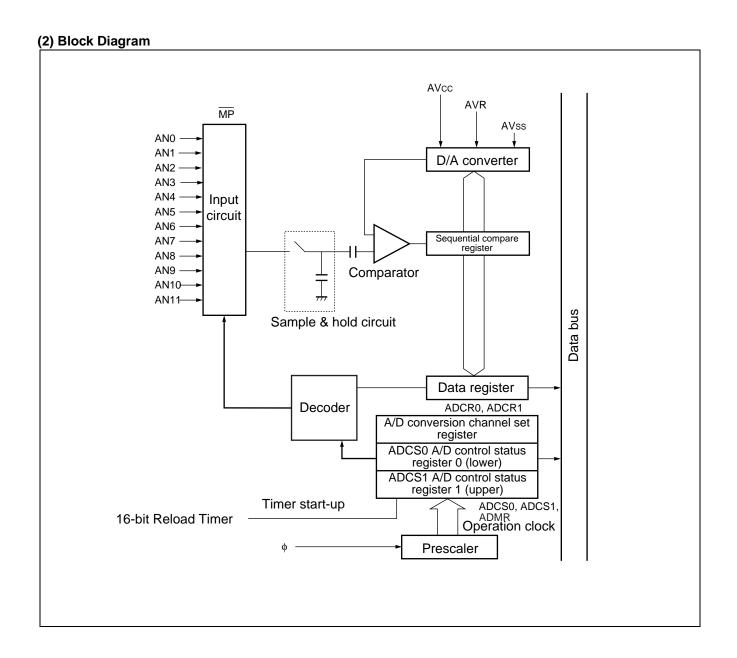

| Par                           | t number                 | MB90V800                                                                                                                                                                                                                                                                                            | MB90F804-101/201                            | MB90802/S              | MB90803/S          |  |  |

|-------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------------------|--------------------|--|--|

| Туре                          |                          | Evaluation FLASH MEMORY products Mask ROM products                                                                                                                                                                                                                                                  |                                             |                        |                    |  |  |

| System clock                  |                          | On-chip PLL clock multiplication method( × 1, × 2, × 3, × 4, 1/2 when PLL stops)  Minimum instruction execution time of 40.0 ns  (at oscillation of 6.25 MHz, four times the PLL clock)                                                                                                             |                                             |                        |                    |  |  |

| ROM capa                      | city                     | No                                                                                                                                                                                                                                                                                                  | 256 KB                                      | 128                    | KB                 |  |  |

| RAM capa                      | city                     | 28 KB                                                                                                                                                                                                                                                                                               | 16 KB                                       | 2 KB                   | 4 KB               |  |  |

| CPU functions                 |                          | Number of basic instructions : 351  Minimum instruction execution time : 40.0 ns/6.25 MHz oscillator (When four times is used : machine clock 25 MHz, Power supply voltage : 3.3 V ± 0.3 V)  Addressing type : 23 types Program Patch Function : 2 address pointers The maximum memory space : 16MB |                                             |                        |                    |  |  |

| Ports                         |                          | not used)                                                                                                                                                                                                                                                                                           | 3 ports (shared with resou                  |                        |                    |  |  |

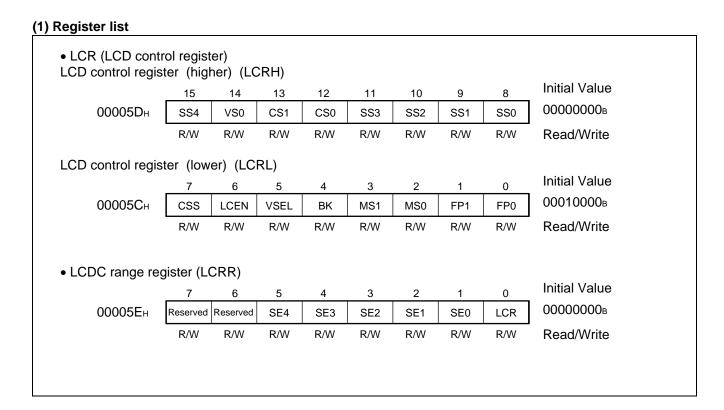

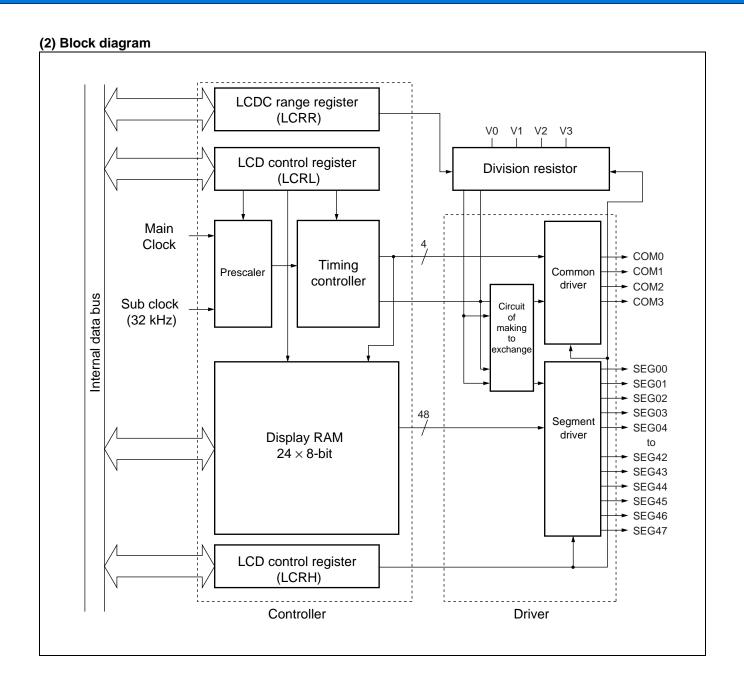

| LCD contro                    | oller/driver             | Segment driver that common driver 48                                                                                                                                                                                                                                                                | t can drive the LCD pane $SEG \times 4$ COM | l (liquid crystal disp | lay) directly, and |  |  |

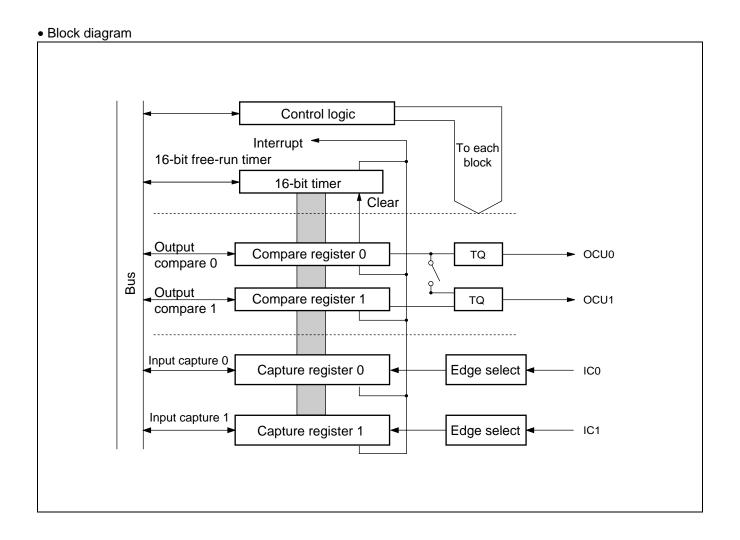

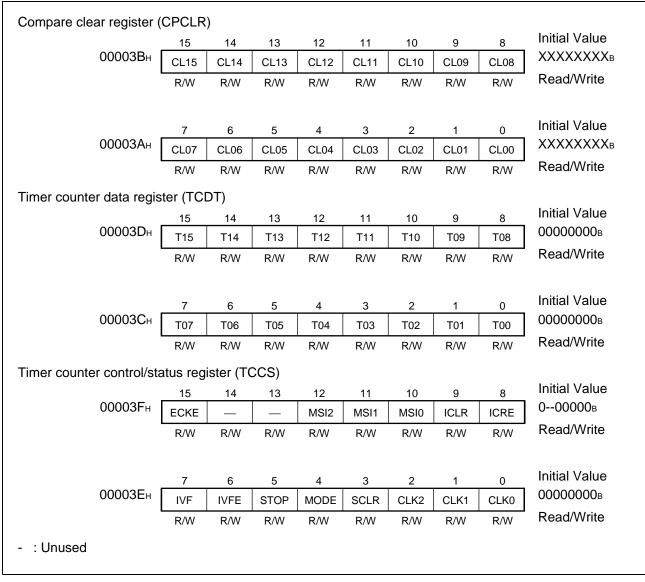

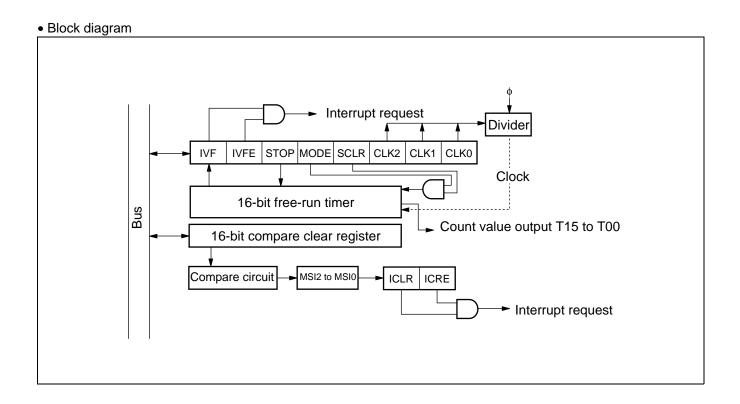

| 16-bit                        | 16-bit free-run<br>timer | 1 channel Overflow interrupt                                                                                                                                                                                                                                                                        |                                             |                        |                    |  |  |

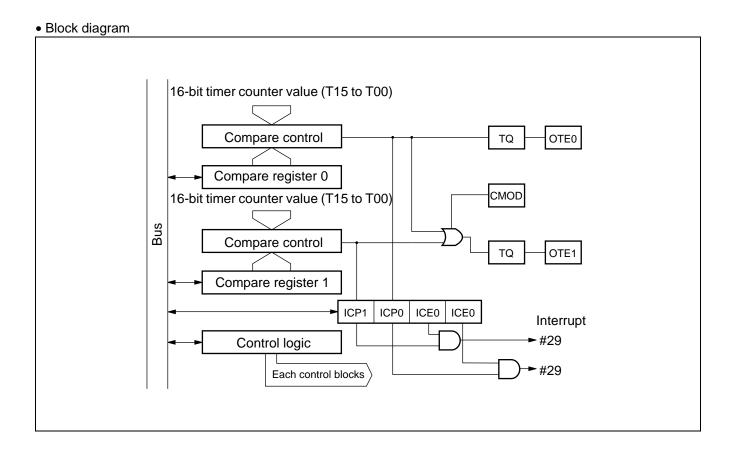

| input/<br>output              | Output compare (OCU)     | 2 channels Pin input factor: matching of the compare register                                                                                                                                                                                                                                       |                                             |                        |                    |  |  |

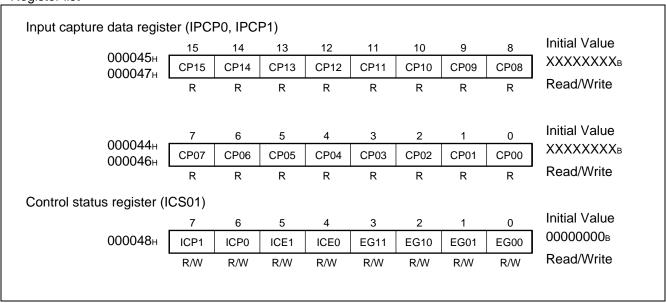

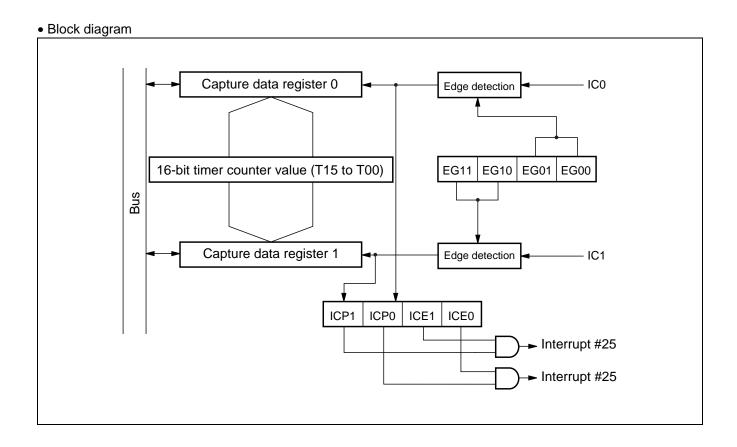

| timer                         | Input capture (ICU)      | 2 channels Rewriting a register value upon a pin input (rising edge, falling edge, or both edges)                                                                                                                                                                                                   |                                             |                        |                    |  |  |

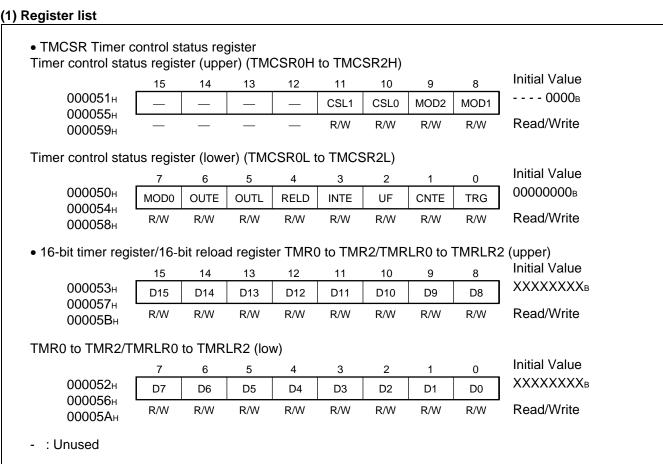

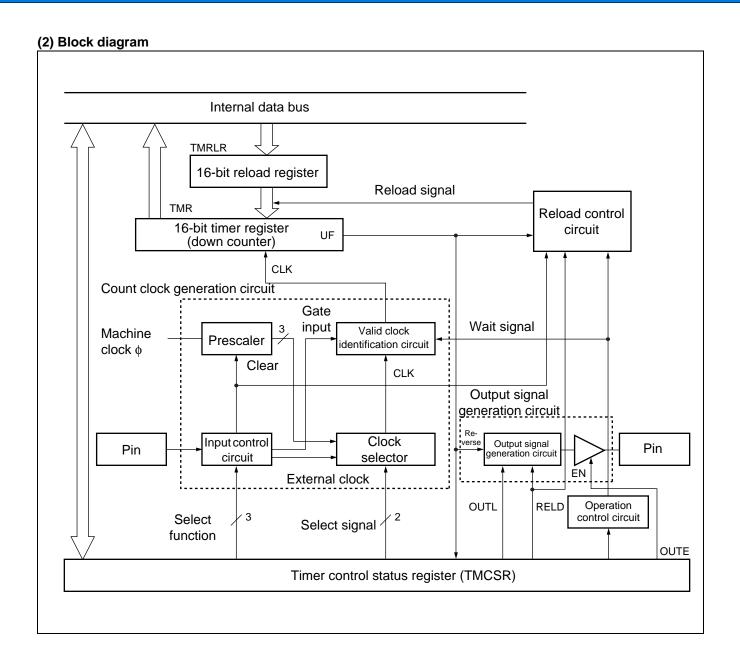

| 16-bit Relo                   | pad Timer                | 16-bit reload timer operation (toggle output, single shot output selectable) The event count function is optional. Three channels are built in.                                                                                                                                                     |                                             |                        |                    |  |  |

| 16-bit PPG                    | 6 timer                  | Output pin × 2 ports Operating clock frequency : fcp, fcp/22, fcp/24, fcp/26 Two channels are built in.                                                                                                                                                                                             |                                             |                        |                    |  |  |

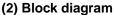

| Timebase                      | timer                    | 1 channel                                                                                                                                                                                                                                                                                           |                                             |                        |                    |  |  |

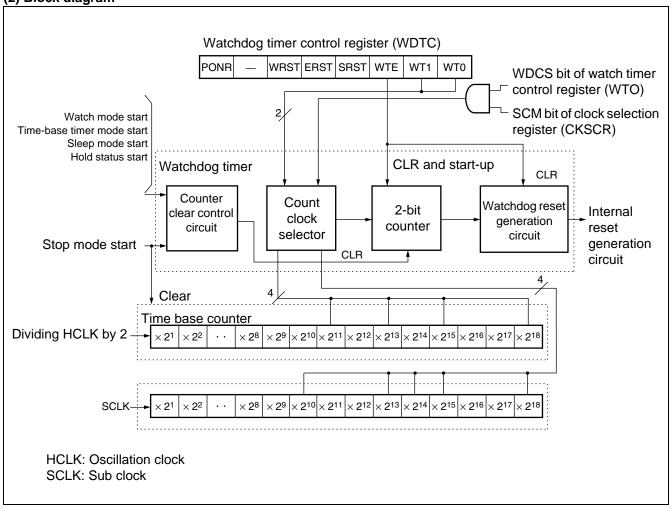

| Watchdog                      | timer                    | 1 channel                                                                                                                                                                                                                                                                                           |                                             |                        |                    |  |  |

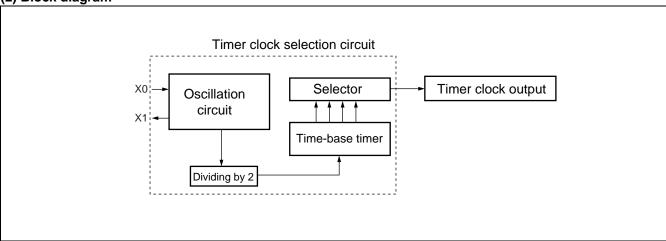

| Timer clock                   | k output circuit         | Clock with a frequency of external input clock divided by 16/32/64/128 can be output externally.                                                                                                                                                                                                    |                                             |                        |                    |  |  |

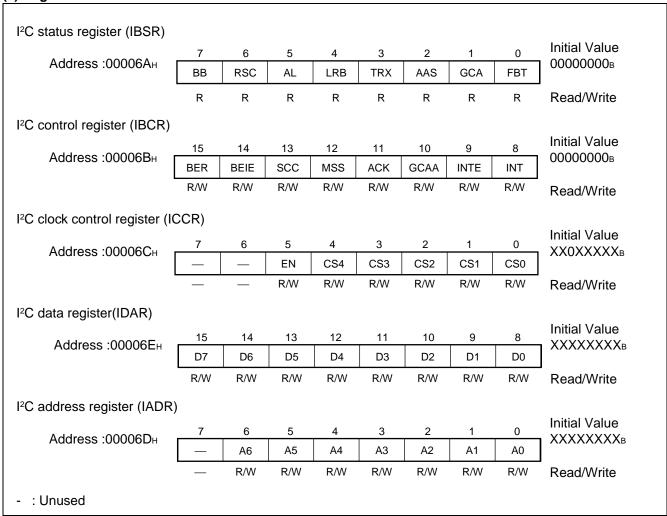

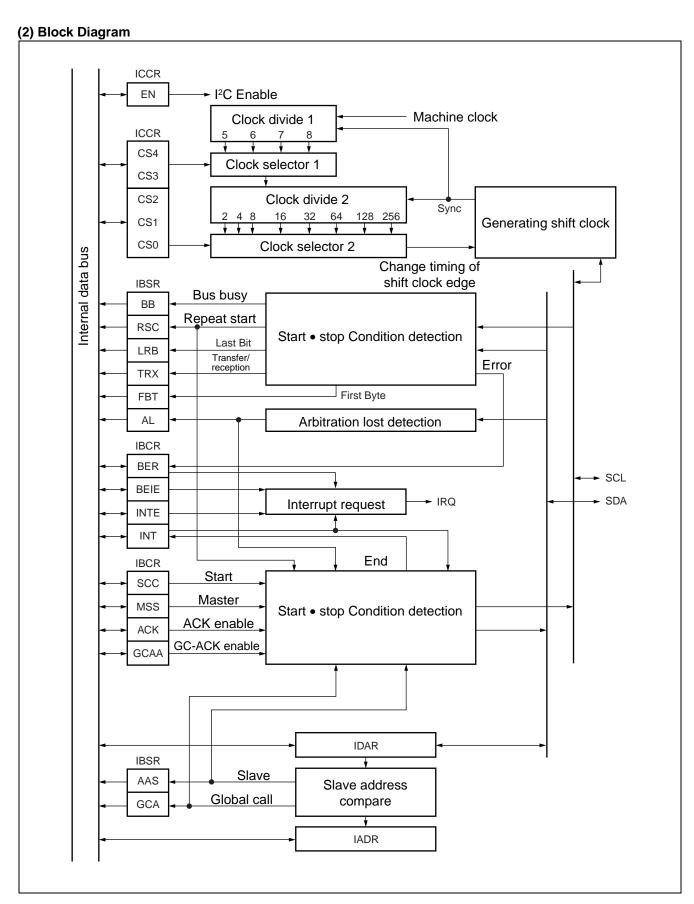

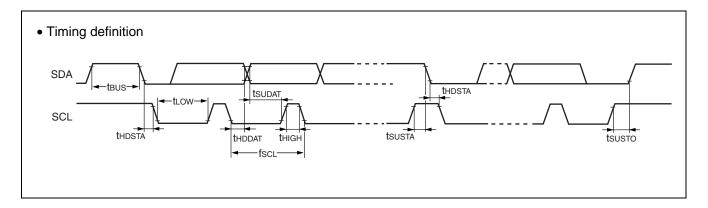

| I <sup>2</sup> C bus          |                          | I <sup>2</sup> C Interface. 1 channel is built-in.                                                                                                                                                                                                                                                  |                                             |                        |                    |  |  |

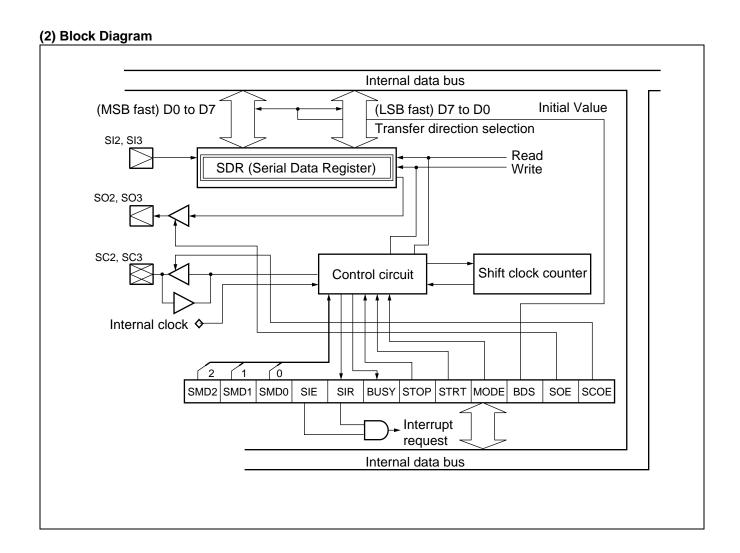

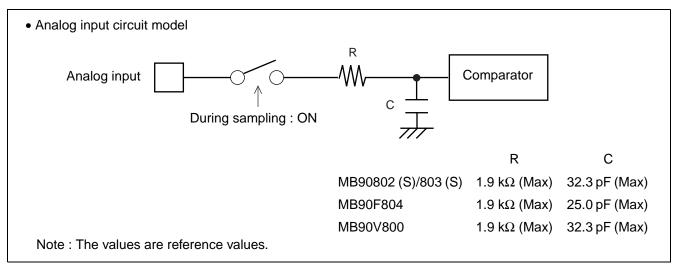

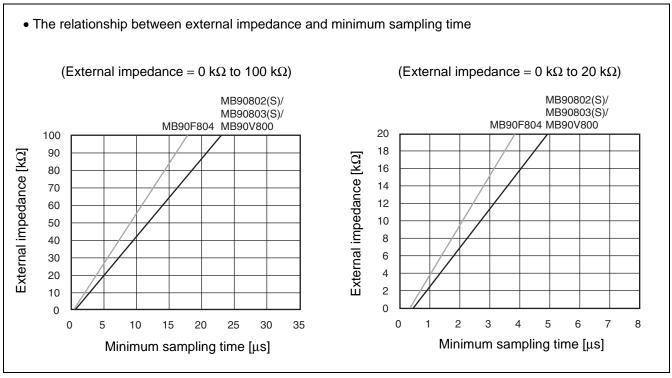

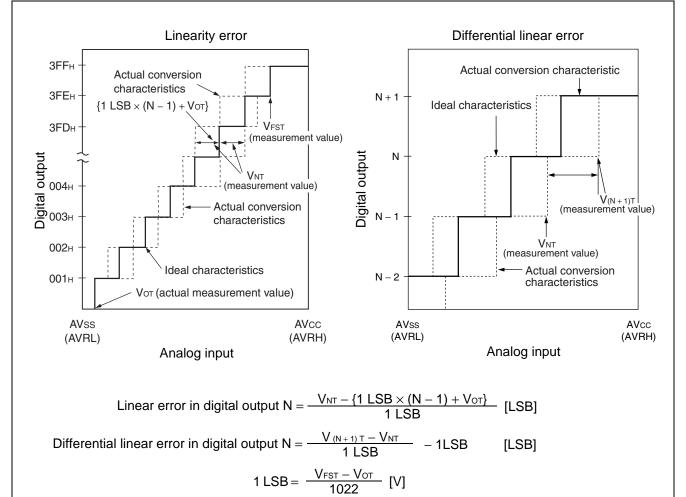

| 8/10-bit A/D converter        |                          | 12 channels (input multiplex) The 8-bit resolution or 10-bit resolution can be set. Conversion time : 5.9 μs (When machine clock 16.8 MHz works).                                                                                                                                                   |                                             |                        |                    |  |  |

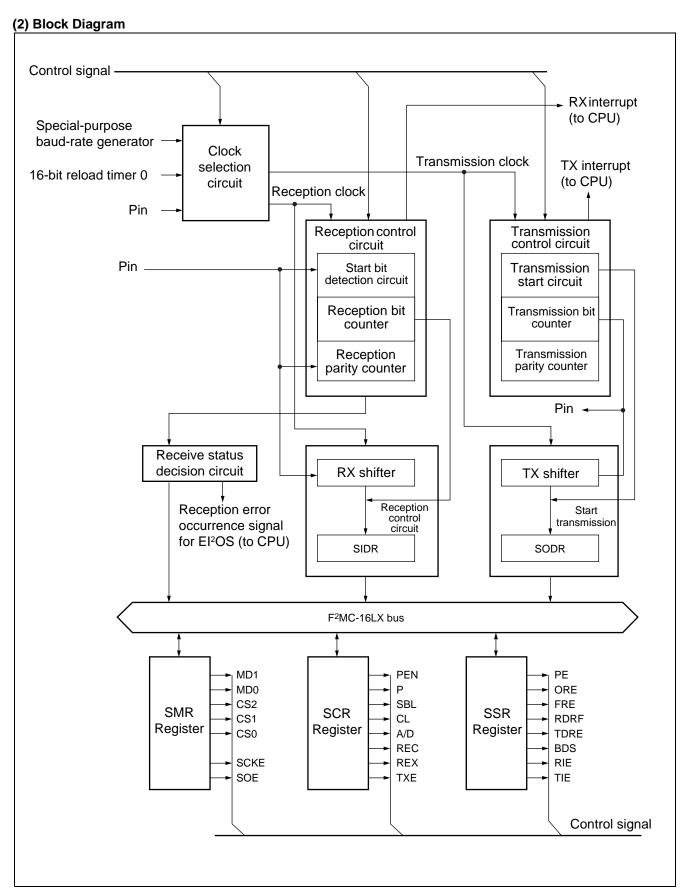

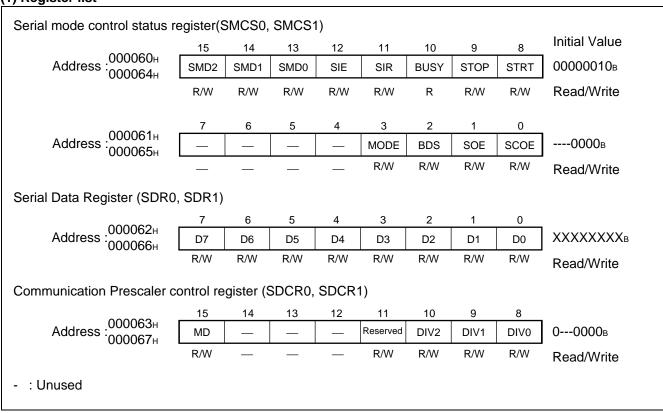

| UART                          |                          | Full-duplex double buffer Asynchronous/synchronous transmit (with start/stop bits) are supported. Two channels are built in.                                                                                                                                                                        |                                             |                        |                    |  |  |

| Extended I/O serial interface |                          | Two channels are built in.                                                                                                                                                                                                                                                                          |                                             |                        |                    |  |  |

| Interrupt de                  | elay interrupt           | Four channel independence (A/D input and using combinedly) Interrupt causes: "L"→"H" edge/"H"→"L" edge/"L" level/"H" level selectable                                                                                                                                                               |                                             |                        |                    |  |  |

| Part number                   | MB90V800                                                                                                                                 | MB90F804-101/201 | MB90803/S |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|--|--|

| DTP/External interrupt        | 8 channels (The 8 channels include with the shared A/D input) Interrupt causes: "L"→"H" edge/"H"→"L" edge/"L" level/"H" level selectable |                  |           |  |  |

| Low Power Consumption<br>Mode | Sleep mode/Time-base timer mode/Watch mode/Stop mode/CPU intermittent mode                                                               |                  |           |  |  |

| Process CMOS                  |                                                                                                                                          |                  |           |  |  |

| Operating voltage             | 2.7 V to 3.6 V                                                                                                                           |                  |           |  |  |

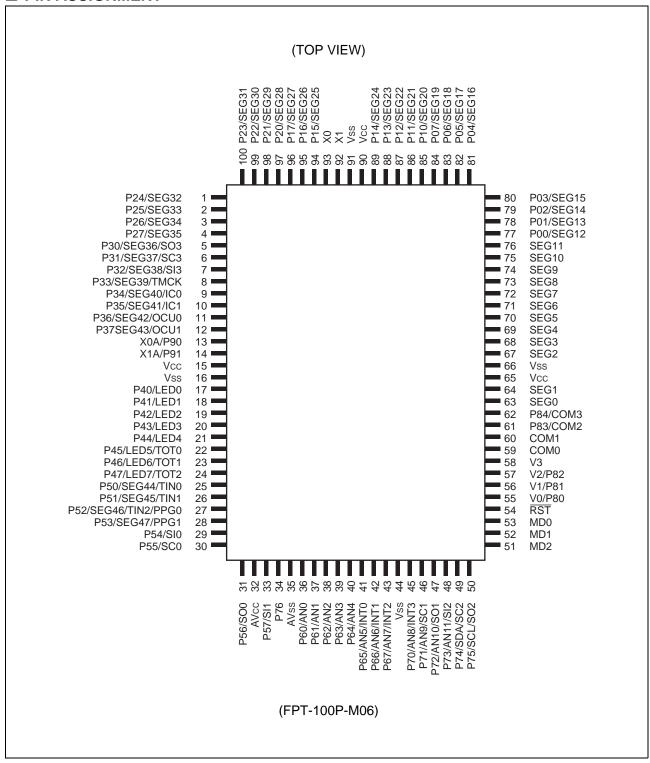

#### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| Pin No.              | Pin Name          | I/O<br>Circuit<br>Type* | Status/function at reset | Function                                                                                                         |

|----------------------|-------------------|-------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------|

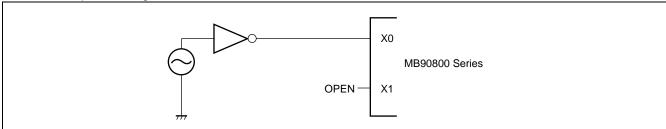

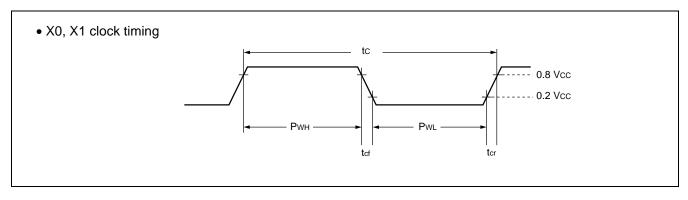

| 92, 93               | X0, X1            | Α                       | Oscillation status       | It is a terminal which connects the oscillator. When connecting an external clock, leave the x1 pin unconnected. |

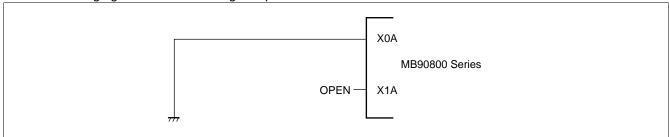

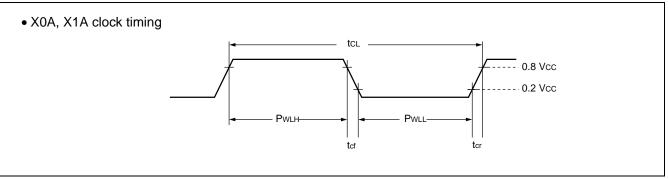

| 13, 14               | X0A, X1A          | В                       | Oscillation status       | It is 32 kHz oscillation pin.<br>(Dual-line model)                                                               |

| 13, 14               | P90, P91          | G                       | Port input<br>(High-Z)   | General purpose input/output port. (Single-line model)                                                           |

| 51                   | MD2               | М                       | Mode Pins                | Input pin for selecting operation mode. Connect directly to Vss.                                                 |

| 52, 53               | MD1, MD0          | L                       | Mode Pins                | Input pin for selecting operation mode. Connect directly to Vcc.                                                 |

| 54                   | RST               | K                       | Reset input              | External reset input pin.                                                                                        |

| 63, 64,<br>67 to 76  | SEG0 to<br>SEG11  | D                       | LCD SEG<br>output        | A segment output terminal of the LCD controller/driver.                                                          |

| 77 to 84             | SEG12 to<br>SEG19 | E                       |                          | A segment output terminal of the LCD controller/driver.                                                          |

|                      | P00 to P07        |                         |                          | General purpose input/output port.                                                                               |

| 85 to 89,            | SEG20 to<br>SEG27 | E                       |                          | A segment output terminal of the LCD controller/driver.                                                          |

| 94 to 96             | P10 to P17        |                         |                          | General purpose input/output port.                                                                               |

| 97 to 100,<br>1 to 4 | SEG28 to<br>SEG35 | E                       |                          | A segment output terminal of the LCD controller/driver.                                                          |

| 1 10 4               | P20 to P27        |                         |                          | General purpose input/output port.                                                                               |

|                      | SEG36             |                         | Port input<br>(High-Z)   | A segment output terminal of the LCD controller/driver.                                                          |

| 5                    | P30               | Е                       |                          | General purpose input/output port.                                                                               |

|                      | SO3               | _                       |                          | Serial data output pin of serial I/O ch.3. Valid when serial data output of serial I/O ch.3 is enabled.          |

|                      | SEG37             |                         |                          | A segment output terminal of the LCD controller/driver.                                                          |

| 6                    | P31               | Е                       |                          | General purpose input/output port.                                                                               |

|                      | SC3               | _                       |                          | Serial clock I/O pin of serial I/O ch.3.<br>Valid when serial clock output of serial I/O ch.3 is<br>enabled.     |

| Pin No.  | Pin Name        | I/O<br>Circuit<br>Type* | Status/function at reset | Function                                                                                                                                     |

|----------|-----------------|-------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|          | SEG38           |                         |                          | A segment output terminal of the LCD controller/driver.                                                                                      |

| 7        | P32             | Е                       |                          | General purpose input/output port.                                                                                                           |

| ,        | SI3             | L                       |                          | Serial data input pin of serial I/O ch.3. This pin may be used during serial I/O ch.3 in input mode, so it cannot use as other pin function. |

|          | SEG39           |                         |                          | A segment output terminal of the LCD controller/driver.                                                                                      |

| 8        | P33             | Е                       |                          | General purpose input/output port.                                                                                                           |

|          | TMCK            |                         |                          | Timer clock output pin. It is effective when permitting the power output.                                                                    |

|          | SEG40,<br>SEG41 | _                       |                          | A segment output terminal of the LCD controller/driver.                                                                                      |

| 9, 10    | P34, P35        | E                       |                          | General purpose input/output port.                                                                                                           |

|          | IC0, IC1        |                         |                          | External trigger input pin of input capture ch.0/ch.1.                                                                                       |

|          | SEG42,<br>SEG43 |                         | Port input<br>(High-Z)   | A segment output terminal of the LCD controller/driver.                                                                                      |

| 11, 12   | P36, P37        | Е                       |                          | General purpose input/output port.                                                                                                           |

|          | OCU0,<br>OCU1   |                         |                          | Output terminal for the Output Compares.                                                                                                     |

| 17 to 21 | LED0 to<br>LED4 | F                       |                          | It is a output terminal for LED (lo∟ = 15 mA).                                                                                               |

|          | P40 to P44      |                         |                          | General purpose input/output port.                                                                                                           |

|          | LED5 to<br>LED7 |                         |                          | It is a output terminal for LED (lo∟ = 15 mA).                                                                                               |

| 00.1.04  | P45 to P47      | _                       |                          | General purpose input/output port.                                                                                                           |

| 22 to 24 | TOT0 to<br>TOT2 | F                       |                          | External event output pin of reload timer ch.0 to ch.2. It is effective when permitting the external event output.                           |

|          | SEG44,<br>SEG45 |                         |                          | A segment output terminal of the LCD controller/driver.                                                                                      |

| 25, 26   | P50, P51        | Е                       |                          | General purpose input/output port.                                                                                                           |

|          | TINO,<br>TIN1   | _                       |                          | External clock input pin of reload timer ch.0, ch.1. It is effective when permitting the external clock input.                               |

| Pin No.  | Pin Name      | I/O<br>Circuit<br>Type* | Status/function at reset | Function                                                                                                                             |

|----------|---------------|-------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|          | SEG46         |                         |                          | A segment output terminal of the LCD controller/driver.                                                                              |

|          | P52           |                         |                          | General purpose input/output port.                                                                                                   |

| 27       | TIN2          | E                       |                          | External clock input pin of reload timer ch.2. It is effective when permitting the external clock input.                             |

|          | PPG0          |                         |                          | PPG timer (ch.0) output pin.                                                                                                         |

| 00       | SEG47         | F                       |                          | A segment output terminal of the LCD controller/driver.                                                                              |

| 28       | P53           | E                       |                          | General purpose input/output port.                                                                                                   |

|          | PPG1          |                         |                          | PPG (ch.1) timer output pin.                                                                                                         |

| 29       | 29 SIO G      |                         |                          | Serial data input pin of UART ch.0. This pin may be used during UART ch.0 in receiving mode, so it cannot use as other pin function. |

|          | P54           |                         | Port input<br>(High-Z)   | General purpose input/output port.                                                                                                   |

| 30       | SC0           | G                       |                          | Serial clock input/output pin of UART ch.0. It is effective when permitting the serial clock output of UART ch.0.                    |

|          | P55           |                         |                          | General purpose input/output port.                                                                                                   |

| 31       | SO0           | G                       |                          | Serial data output pin of UART ch.0. It is effective when permitting the serial clock output of UART ch.0.                           |

|          | P56           |                         |                          | General purpose input/output port.                                                                                                   |

| 33       | SI1           | G                       |                          | Serial data input pin of UART ch.1. This pin may be used during UART ch.1 in receiving mode, so it cannot use as other pin function. |

|          | P57           |                         |                          | General purpose input/output port.                                                                                                   |

| 34       | P76           | G                       |                          | General purpose input/output port.                                                                                                   |

| 36 to 40 | AN0 to<br>AN4 | 1                       |                          | Analog input pin ch.0 to ch.4 of A/D converter. Enabled when analog input setting is " enabled "(set by ADER).                       |

|          | P60 to P64    |                         |                          | General purpose input/output port.                                                                                                   |

| Pin No.  | Pin Name        | I/O<br>Circuit<br>Type* | Status/function at reset | Function                                                                                                                                     |

|----------|-----------------|-------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|          | AN5 to<br>AN7   |                         |                          | Analog input pin ch.5 to ch.7 of A/D converter. Enabled when analog input setting is " enabled ".                                            |

| 41 to 43 | P65 to P67      | I                       |                          | General purpose input/output port.                                                                                                           |

|          | INT0 to<br>INT2 |                         | Analog input<br>(High-Z) | Functions as an external interrupt ch.0 to ch.2 input pin.                                                                                   |

|          | AN8             |                         |                          | Analog input pin ch.8 of A/D converter. Enabled when analog input setting is " enabled ".                                                    |

| 45       | P70             | I                       |                          | General purpose input/output port.                                                                                                           |

|          | INT3            |                         |                          | Functions as an external interrupt ch.3 input pin.                                                                                           |

|          | AN9             |                         |                          | Analog input pin ch.9 of A/D converter. Enabled when analog input setting is " enabled ".                                                    |

| 46       | P71             | ı                       |                          | General purpose input/output port.                                                                                                           |

|          | SC1             |                         |                          | Serial clock input/output pin of UART ch.1. It is effective when permitting the serial clock output of UART ch.1.                            |

|          | AN10            |                         |                          | Analog input pin ch.10 of A/D converter. Enabled when analog input setting is " enabled ".                                                   |

| 47       | P72             | 1                       | Port input               | General purpose input/output port.                                                                                                           |

| 47       | SO1             | •                       | (High-Z)                 | Serial data output pin of serial I/O ch.1. Valid when serial data output of serial I/O ch.1 is enabled.                                      |

|          | AN11            |                         |                          | Analog input pin ch.11 of A/D converter. Enabled when analog input setting is " enabled ".                                                   |

| 48       | P73             | 1                       |                          | General purpose input/output port.                                                                                                           |

|          | SI2             | •                       |                          | Serial data input pin of serial I/O ch.2. This pin may be used during serial I/O ch.2 in input mode, so it cannot use as other pin function. |

| Pin No.           | Pin Name      | I/O<br>Circuit<br>Type* | Status/function at reset | Function                                                                                                                                                                                                        |

|-------------------|---------------|-------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

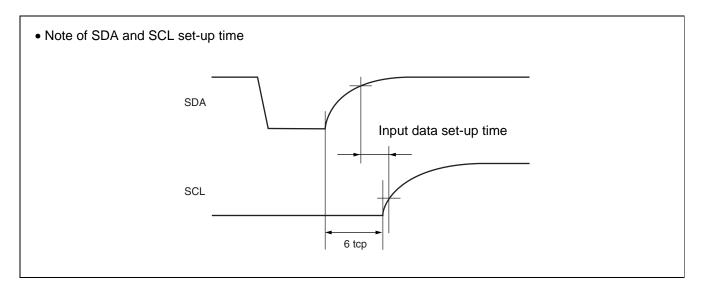

|                   | SDA           |                         |                          | Data input/output pin of I <sup>2</sup> C Interface. This pin is enabled when the I <sup>2</sup> C interface is operated. While the I <sup>2</sup> C interface is running, the port must be set for input use.  |

| 49                | P74           | Н                       |                          | General purpose input/output port. (N-ch open-drain, withstand voltage of 5 V.)                                                                                                                                 |

|                   | SC2           |                         | Port input               | Serial clock input pin of serial I/O ch.2.<br>Valid when serial clock output of serial I/O ch.2 is<br>enabled.                                                                                                  |

|                   | SCL           |                         | (High-Z)                 | Clock input/output pin of I <sup>2</sup> C Interface. This pin is enabled when the I <sup>2</sup> C interface is operated. While the I <sup>2</sup> C interface is running, the port must be set for input use. |

| 50                | P75           | Н                       |                          | General purpose input/output port. (N-ch open-drain, withstand voltage of 5 V.)                                                                                                                                 |

|                   | SO2           |                         |                          | Serial data output pin of serial I/O ch.2.<br>Valid when serial data output of serial I/O ch.2 is<br>enabled.                                                                                                   |

| 55 to 57          | 22 1() 2/     |                         | LCD drive power          | LCD controller/driver. Reference power terminals of LCD controller/driver.                                                                                                                                      |

|                   | P80 to P82    |                         | supply input             | General purpose input/output port.                                                                                                                                                                              |

| 59, 60            | COM0,<br>COM1 | D                       | LCD COM output           | A common output terminal of the LCD controller/driver.                                                                                                                                                          |

|                   | P83, P84      |                         | Port input               | General purpose input/output port.                                                                                                                                                                              |

| 61, 62            | COM2,<br>COM3 | E                       | (High-Z)                 | A common output terminal of the LCD controller/driver.                                                                                                                                                          |

| 32                | AVcc          | С                       |                          | A/D converter exclusive power supply input pin.                                                                                                                                                                 |

| 35                | AVss          | С                       |                          | A/D converter-exclusive GND power supply pin.                                                                                                                                                                   |

| 58                | V3            | J                       | Power supply             | LCD controller/driver Reference power terminals of LCD controller/driver.                                                                                                                                       |

| 15, 65, 90        | Vcc           | _                       |                          | These are power supply input pins.                                                                                                                                                                              |

| 16, 44,<br>66, 91 | Vss           |                         |                          | GND power supply pin.                                                                                                                                                                                           |

<sup>\* :</sup> Refer to "■ I/O CIRCUIT TYPE" for I/O circuit type.

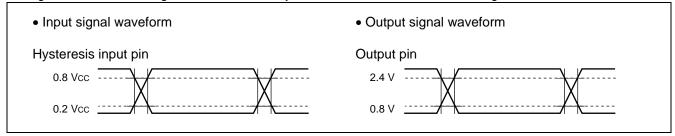

### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                         | Remarks                                                                                |

|------|-------------------------------------------------|----------------------------------------------------------------------------------------|

| А    | Clock input  N-ch  N-ch  Standby control signal | Oscillation feedback resistance : 1 $\mbox{M}\Omega$ approx.                           |

| В    | Clock input  N-ch  N-ch  Standby control signal | Low-rate oscillation feedback resistor, approx.10 $\text{M}\Omega$                     |

| С    | P-ch AVP                                        | Analog power supply input protection circuit                                           |

| D    | P-ch R LCDC output                              | LCDC output                                                                            |

| E    | LCDC output Input signal Standby control signal | CMOS output LCDC output Hysteresis input (With input interception function at standby) |

| Туре | Circuit                                                        | Remarks                                                                                                                                                                                                                                                                                                                                                         |

|------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F    | P-ch N-ch Input signal Standby control signal                  | CMOS output     (Heavy-current IoL =15 mA for LED drive)     Hysteresis input     (With input interception function at standby)                                                                                                                                                                                                                                 |

| G    | N-ch Input signal Standby control signal                       | CMOS output CMOS hysteresis input (With input interception function at standby)  Notes: • The I/O port and internal resources share one output buffer for their outputs.  The I/O port and internal resources share one input buffer for their input.                                                                                                           |

| н    | N-ch Nout    Table   Nout   Signal   Standby control signal    | <ul> <li>Hysteresis input (With input interception function at standby)</li> <li>N-ch open drain output</li> </ul>                                                                                                                                                                                                                                              |

| I    | Input signal Standby control signal A/D converter Analog input | CMOS output CMOS hysteresis input (With input interception function at standby) Analog input (If the bit of analog input enable register = 1, the analog input of A/D converter is enabled.)  Notes: The I/O port and internal resources share one output buffer for their outputs. The I/O port and internal resources share one input buffer for their input. |

| Туре | Circuit                                                                   | Remarks                                                                                                      |

|------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| J    | P-ch N-ch N-ch Input signal Standby control signal LCD drive power supply | CMOS output CMOS hysteresis input (With input interception function at standby) LCD drive power supply input |

| К    | Reset input                                                               | CMOS hysteresis input with pull-up resistor.                                                                 |

| L    | Reset input                                                               | CMOS hysteresis input                                                                                        |

| М    | Input                                                                     | CMOS hysteresis input with pull-down resistor                                                                |

#### **■ HANDLING DEVICES**

#### 1. Preventing Latch-up, Turning on Power Supply

Latch-up may occur on CMOS IC under the following conditions:

- If a voltage higher than Vcc or lower than Vss is applied to input and output pins,

- A voltage higher than the rated voltage is applied between Vcc pin and Vss pin.

- If the AVcc power supply is turned on before the Vcc voltage.

Ensure that you apply a voltage to the analog power supply at the same time as  $V_{CC}$  or after you turn on the digital power supply (when you perform power-off, turn off the analog power supply first or at the same time as  $V_{CC}$  and the digital power supply).

When latch-up occurs, power supply current increases rapidly and might thermally damage elements. When using CMOS IC, take great care to prevent the occurrence of latch-up.

#### 2. Treatment of unused pins

If unused input pins are left open, they may cause abnormal operation or latch-up which may lead to permanent damage to the semiconductor. Any such pins should be pulled up or pulled down through resistance of at least  $2 \text{ k}\Omega$ .

Any unused input/output pins should be left open in output status, or if found set to input status, they should be treated in the same way as input pins.

Any unused output pins should be left open.

#### 3. Treatment of A/D converter power supply pins

Even if the A/D converter is not used, pins should be connected so that AVcc = Vcc, and AVss = Vss.

#### 4. About the attention when the external clock is used

In using an external clock, drive pin X0 only and leave pin X1 open.

The example of using an external clock is shown below.

Please set X0A = GND and X1A = open without subclock mode.

The following figure shows the using sample.

#### 5. Treatment of power supply pins (Vcc/Vss)

In products with multiple Vcc or Vss pins, the pins of the same potential are internally connected in the device to avoid abnormal operations including latch-up. However, you must connect all power supply pins to external power supply and a ground line to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with the Vcc and Vss pins of this device at the low impedance.

It is also advisable to connect a ceramic capacitor of approximately 0.1  $\mu$ F as a bypass capacitor between Vcc and Vss near this device.

#### 6. About Crystal oscillators circuit

Noise near the X0/X1 pins and X0A/X1A pins may cause the device to malfunction. Design the printed circuit board so that X0/X1 pins and X0A/X1A pins, the crystal oscillator (or the ceramic oscillator) and the bypass capacitor to ground are located as close to the device as possible.

It is strongly recommended to design the PC board artwork with the X0/X1 pins and X0A/X1A pins surrounded by ground plane because stable operation can be expected with such a layout.

Please ask the crystal maker to evaluate the oscillational characteristics of the crystal and this device.

#### 7. Caution on Operations during PLL Clock Mode

On this microcontroller, if in case the crystal oscillator breaks off or an external reference clock input stops while the PLL clock mode is selected, a self-oscillator circuit contained in the PLL may continue its operation at its self-running frequency. However, Fujitsu will not guarantee results of operations if such failure occurs.

#### 8. Stabilization of Supply Power Supply

A sudden change in the supply voltage may cause the device to malfunction even within the  $V_{CC}$  supply voltage operating range. Therefore, the  $V_{CC}$  supply voltage should be stabilized. For reference, the supply voltage should be controlled so that  $V_{CC}$  ripple variations (peak- to-peak values) at commercial frequencies (50 MHz/60 MHz) fall below 10% of the standard  $V_{CC}$  supply voltage and the coefficient of fluctuation does not exceed 0.1 V/ms at instantaneous power switching.

#### 9. Note on Using the two-subsystem product as one-subsystem product

If you are using only one subsystem of the MB90800 series that come in one two-subsystem product, use it with  $XOA = V_{SS}$  and X1A = OPEN.

#### 10. Write to FLASH

Ensure that you must write to FLASH at the operating voltage Vcc = 3.0 V to 3.6 V.

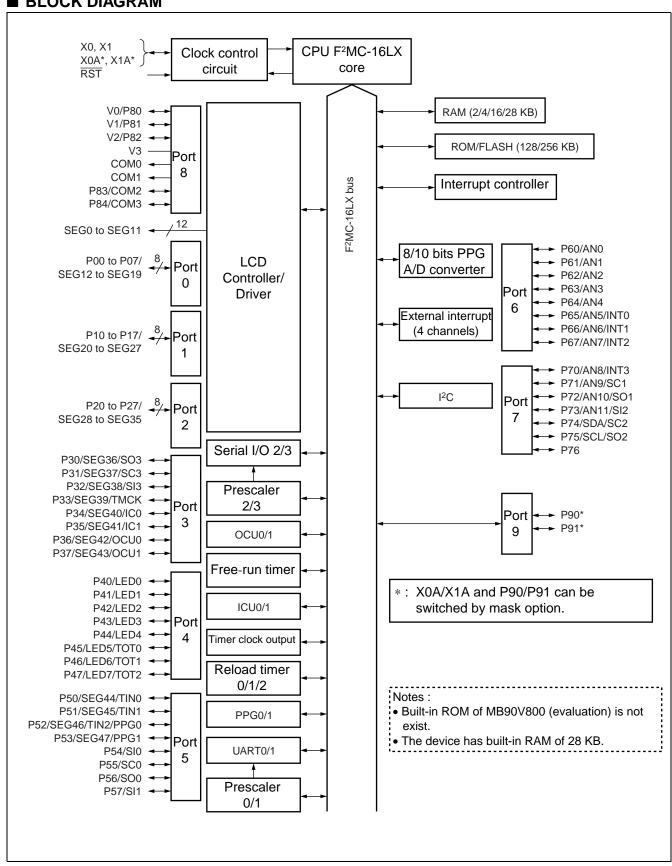

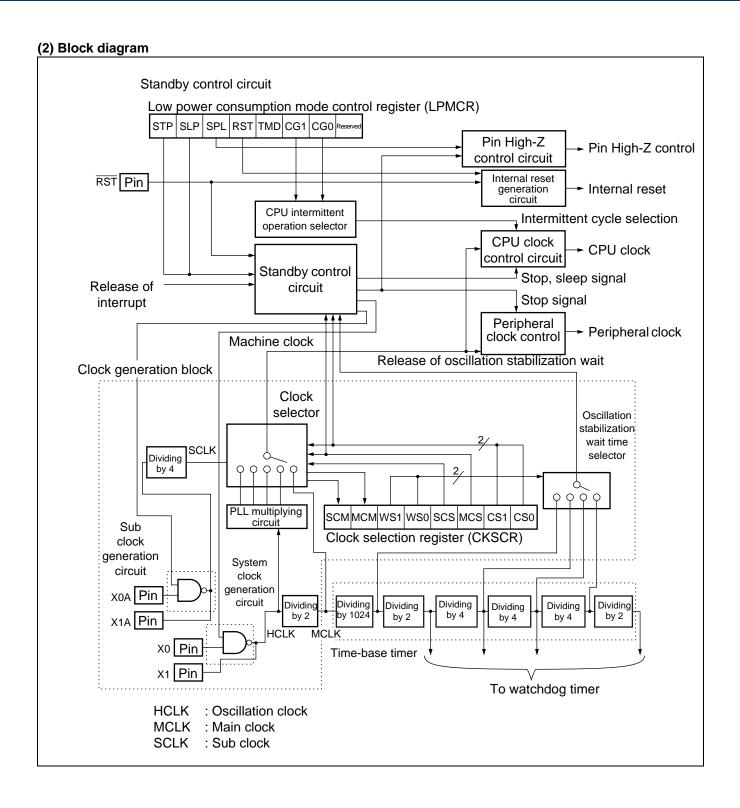

#### **■ BLOCK DIAGRAM**

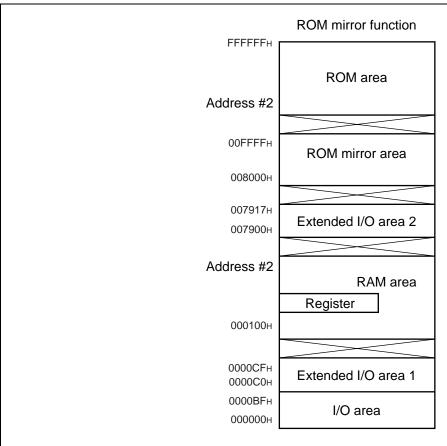

#### ■ MEMORY MAP

| Part number | Address #1 | Address #2            |

|-------------|------------|-----------------------|

| MB90802     | 0008FFн    | FE0000н               |

| MB90803     | 0010FFн    | FE0000н               |

| MB90F804    | 0040FFн    | FC0000н               |

| MB90V800    | 0070FFн    | F80000 <sub>H</sub> * |

<sup>\*:</sup> ROM is not built into MB90V800. F80000<sub>H</sub> is ROM decipherment region on the tool side.

#### Memory Map of MB90800 Series

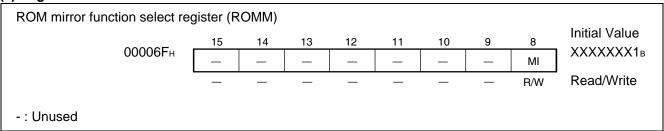

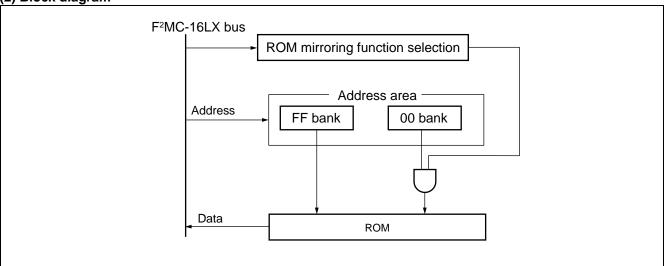

Notes: • When the ROM mirror function register has been set, the mirror image data at higher addresses ("FF4000H to FFFFFH") of bank FF is visible from the higher addresses ("008000H to 00FFFFH") of bank 00.

- The ROM mirror function is for using the C compiler small model.

- The lower 16-bit addresses of bank FF are equivalent to those of bank 00. Note that because the ROM area of bank FF exceeds

- 32 KB, all data in the ROM area cannot be shown in mirror image in bank 00.

- When the C compiler small model is used, the data table can be shown as mirror image at " 008000H to 00FFFFH " by storing the data table at " FF8000H to FFFFFFH. Therefore, data tables in the ROM area can be referenced without declaring the far addressing with the pointer.

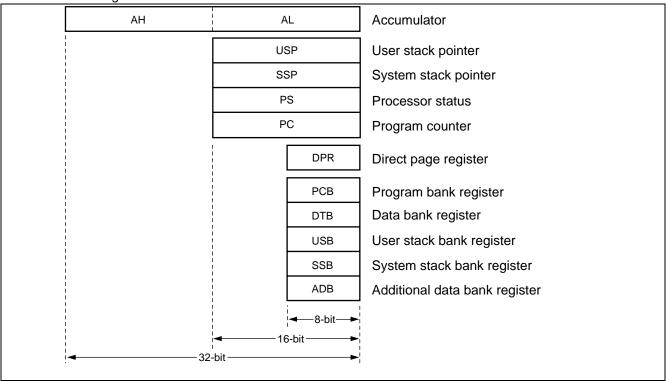

### ■ F<sup>2</sup>MC-16L CPU Programming model

• Dedicated Registers

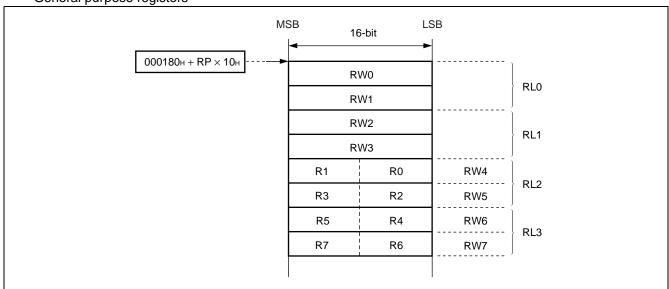

• General purpose registers

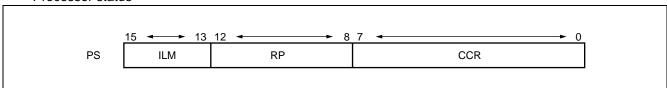

#### Processor status

### ■ I/O MAP

| Address                  | Register abbreviation | Register                                 | Read/<br>Write | Resource name | Initial Value                |

|--------------------------|-----------------------|------------------------------------------|----------------|---------------|------------------------------|

| 000000н                  | PDR0                  | Port 0 data register                     | R/W            | Port 0        | XXXXXXXXB                    |

| 000001н                  | PDR1                  | Port 1 data register                     | R/W            | Port 1        | XXXXXXXXB                    |

| 000002н                  | PDR2                  | Port 2 data register                     | R/W            | Port 2        | XXXXXXXXB                    |

| 000003н                  | PDR3                  | Port 3 data register                     | R/W            | Port 3        | XXXXXXXX                     |

| 000004н                  | PDR4                  | Port 4 data register                     | R/W            | Port 4        | XXXXXXXX                     |

| 000005н                  | PDR5                  | Port 5 data register                     | R/W            | Port 5        | XXXXXXXX                     |

| 000006н                  | PDR6                  | Port 6 data register                     | R/W            | Port 6        | XXXXXXXX                     |

| 000007н                  | PDR7                  | Port 7 data register                     | R/W            | Port 7        | - XXXXXXXB                   |

| 000008н                  | PDR8                  | Port 8 data register                     | R/W            | Port 8        | XXXXXB                       |

| 000009н                  | PDR9                  | Port 9 data register                     | R/W            | Port 9        | XX <sub>B</sub>              |

| 00000Ан<br>to<br>00000Fн |                       | Prohib                                   | ited           |               |                              |

| 000010н                  | DDR0                  | Port 0 direction register                | R/W            | Port 0        | 00000000                     |

| 000011н                  | DDR1                  | Port 1 direction register                | R/W            | Port 1        | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000012н                  | DDR2                  | Port 2 direction register                | R/W            | Port 2        | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000013н                  | DDR3                  | Port 3 direction register                | R/W            | Port 3        | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000014н                  | DDR4                  | Port 4 direction register                | R/W            | Port 4        | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000015н                  | DDR5                  | Port 5 direction register                | R/W            | Port 5        | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000016н                  | DDR6                  | Port 6 direction register                | R/W            | Port 6        | 0 0 0 0 0 0 0 0 <sub>B</sub> |

| 000017н                  | DDR7                  | Port 7 direction register                | R/W            | Port 7        | - 0 0 0 0 0 0 0в             |

| 000018н                  | DDR8                  | Port 8 direction register                | R/W            | Port 8        | 00000                        |

| 000019н                  | DDR9                  | Port 9 direction register                | R/W            | Port 9        | О Ов                         |

| 00001Ан<br>to<br>00001Dн |                       | Prohib                                   | ited           |               |                              |

| 00001Бн<br>00001Ен       | ADER0                 | Analog input enable 0                    | R/W            | Port 6, A/D   | 1111111 <sub>B</sub>         |

| 00001Eн                  | ADER1                 | Analog input enable 1                    | R/W            | Port 7, A/D   | 1111в                        |

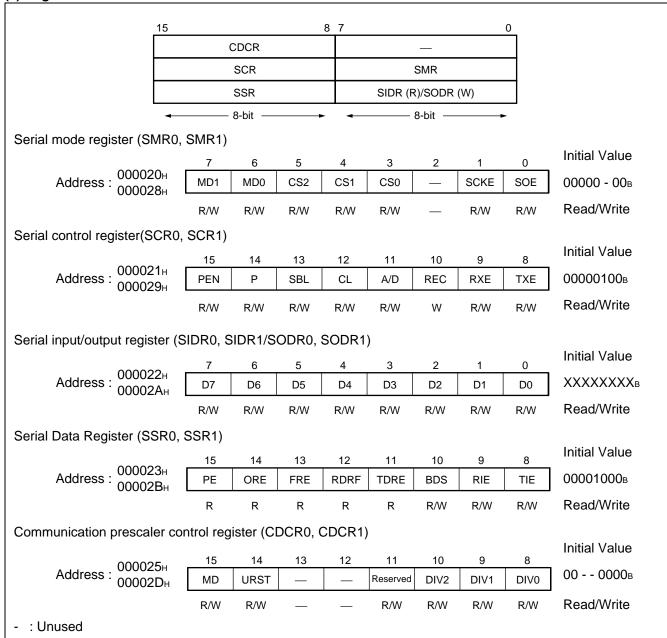

| 000020н                  | SMR0                  | Serial mode register                     | R/W            | ,             | 0 0 0 0 0 - 0 Ов             |

| 000021н                  | SCR0                  | Serial control register                  | R/W            |               | 00000100в                    |

| 000022н                  | S1DR0/<br>SODR0       | Serial input/output register R/W UARTO   |                | XXXXXXXXB     |                              |

| 000023н                  | SSR0                  | Serial data register                     | R/W            |               | 0 0 0 0 10 0 0в              |

| 000024н                  |                       | Prohib                                   | ited           |               |                              |

| 000025н                  | CDCR0                 | Communication prescaler control register | R/W            | Prescaler 0   | 000000в                      |

| 000026н,<br>000027н      |                       | Prohib                                   | ited           |               |                              |

| 000028-b   SMR1   Serial mode register   R/W   000029-b   SCR1   Serial control register   R/W   W   W   W   W   W   W   W   W   W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Address | Register abbreviation | Register                            | Read/<br>Write | Resource name      | Initial Value      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|-------------------------------------|----------------|--------------------|--------------------|

| SIDR1/ SORM   Serial input/output register   R/W   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 000028н | SMR1                  | Serial mode register                | R/W            |                    | 0 0 0 0 0 - 0 0в   |

| SODR1   Sciral linput/output register   R/W   | 000029н | SCR1                  | Serial control register             | R/W, W         |                    | 00000100в          |

| O0002CH   CDCR1   Communication prescaler control   R/W   Prescaler 1   0 0 - 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00002Ан |                       | Serial input/output register        | R/W            | UART1              | XXXXXXXXB          |

| CDCR1   Communication prescaler control register   R/W   Prescaler 1   0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 00002Вн | SSR1                  | Serial data register                |                | 00001000в          |                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 00002Сн |                       | Prohibite                           | ed             |                    |                    |

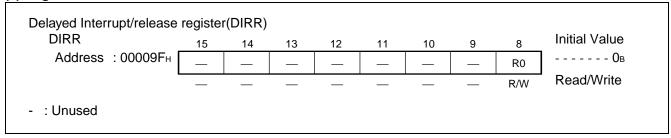

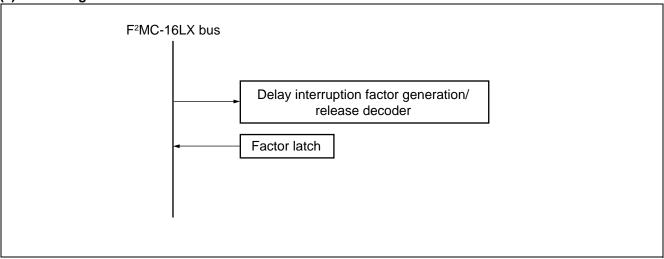

| 00002FH   000030h   ENIR   Interrupt/DTP enable   R/W   External interrupt   0000030h   EIRR   Interrupt/DTP source   R/W   0000030h   EIRR   Interrupt/DTP source   R/W   0000030h   EIRR   Request level set register   Prohibited   Prohibited   0000030h   ADCS0   Control status register (lower)   R/W   0000030h   ADCS1   Control status register (upper)   R/W   W, R/W   000036h   ADCR0   Data register (upper)   R/W   R/W   000036h   ADCR1   Data register (upper)   R/W   Prohibited   Prohibited   Data register (upper)   R/W   (upper)    | 00002Dн | CDCR1                 | ·                                   | R/W            | Prescaler 1        | 000000в            |

| 00002FH         ENIR         Interrupt/DTP enable         R/W         External interrupt        0008           000030H         EIRR         Interrupt/DTP source         R/W         External interrupt        0008           000032H         ELVR         Request level set register         R/W         0000030         0000000         0000000           000034H         ADCS0         Control status register (lower)         R/W         ADCS1         Control status register (upper)         W, R/W         ADCS1         00000000         0000000         00000000         00000000         00000000         00000000         00000000         00000000         00000000         00000000         00000000         00000000         00000000         00000000         000000000         00000000         00000000         000000000         000000000         000000000         000000000         000000000         000000000         00000000         000000000         000000000         00000000000         000000000         000000000         000000000         000000000         00000000         000000000         000000000         0000000000         000000000         000000000         000000000         000000000         000000000         000000000         0000000000         000000000000         00000000000         00000000000 <t< td=""><td>00002Ен</td><td></td><td>Prohibite</td><td>2d</td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00002Ен |                       | Prohibite                           | 2d             |                    |                    |

| O00031                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00002Fн |                       | 1 Tornibile                         | <del>J</del> u |                    |                    |

| O00032H   ELVR   Request level set register   R/W   O00000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 000030н | ENIR                  | Interrupt/DTP enable                | R/W            |                    | ООООВ              |

| 000033H         ADCS0         Control status register (lower)         R/W         A/D converter         0000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 000031н | EIRR                  | Interrupt/DTP source                | R/W            | External interrupt | XXXX <sub>B</sub>  |

| 000034+ih         ADCS0         Control status register (lower)         R/W         R/W         ADCS1         Control status register (upper)         W, R/W         ADCS1         Control status register (upper)         W, R/W         ADCS1         Control status register (upper)         W, R/W         ADCS0         Data register (lower)         R, W         ADCS0         Data register (upper)         R, W         ADCS0         ADCS0         Data register (upper)         R/W         ADCS0         ADCS0         ADCS0         Data register (upper)         R/W         ADCS0         ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 000032н | ELVR                  | Request level set register          | R/W            |                    | 0 0 0 0 0 0 0 0в   |